# Improving KVM x86 Nested Virtualization

#### Who am I?

- Architect at OCI (Oracle Cloud Infrastructure)

- ~4 years of Virtualization, SDN and Cloud Computing

- ~7 years of cyber R&D in PMO & IDF

- Active KVM nVMX contributor

- Interests: Anything low-level

- o CPU, OS internals, networking, vulnerabilities, exploits, virtualization and etc.

- Twitter: @Liran\_Alon

#### **Outline**

- Focus only on nVMX (Sorry AMD...)

- Deep-dive into one nVMX mechanism which had many issues

- First documentation of mechanism outside code

- Maybe relevant for other architectures nested support

- Present recent nVMX improvements in high-level

- Highlight nVMX open issues

- Suggest possible nVMX future directions

## How does nVMX works?

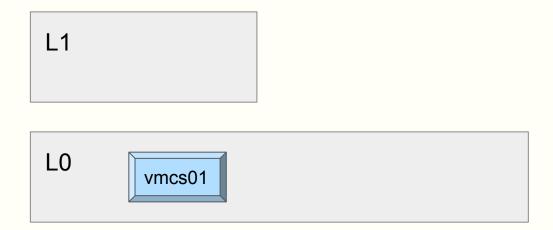

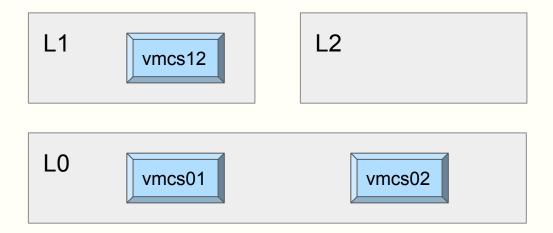

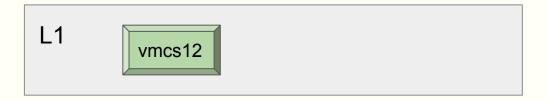

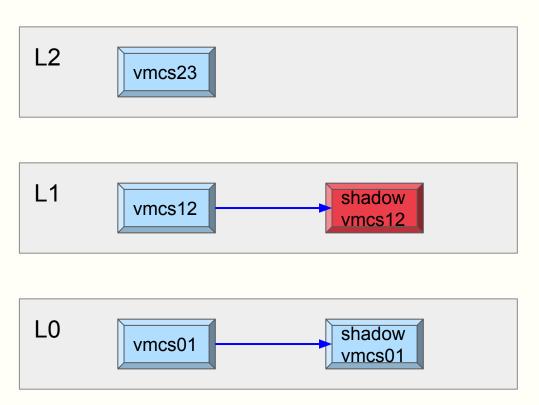

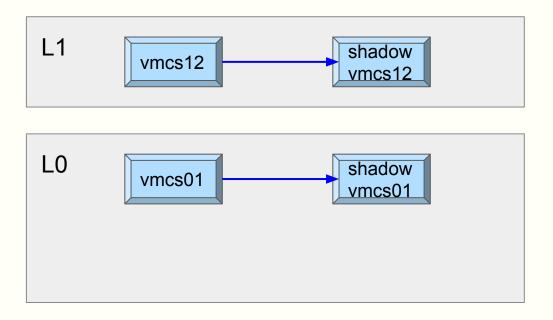

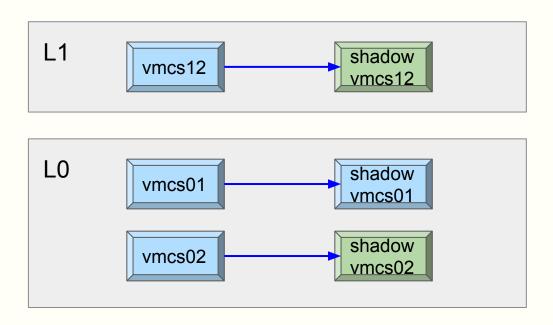

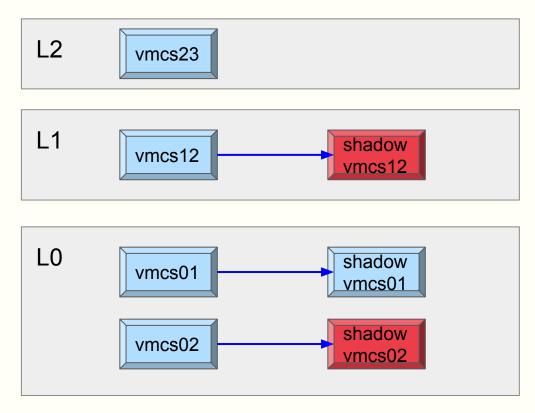

#### L0 runs L1 with vmcs01

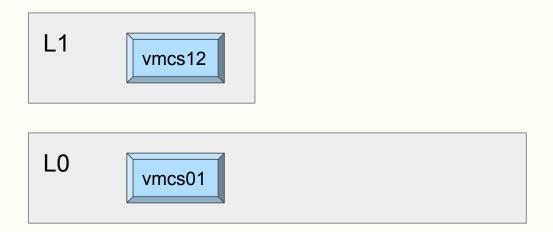

## L1 creates vmcs12 for running L2

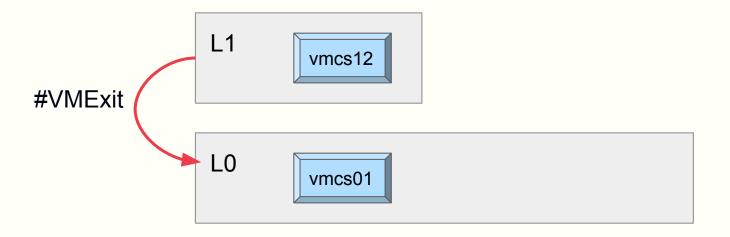

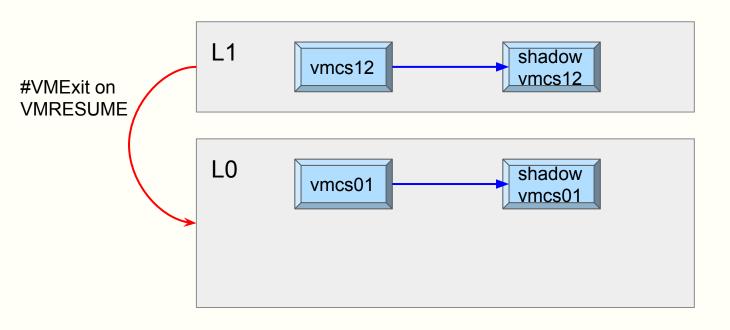

## L1's VMRESUME triggers VMExit to L0

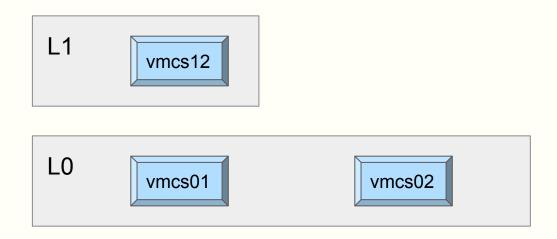

## L0 merges vmcs01 & vmcs12 to vmcs02

#### L0 runs L2 with vmcs02

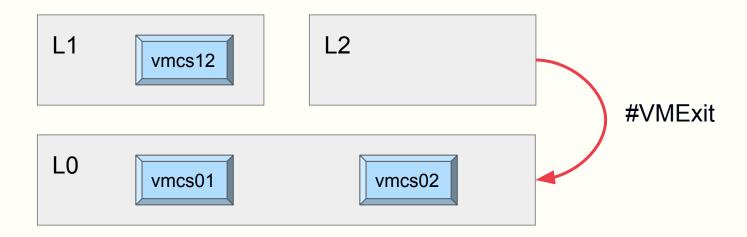

## L2 runs until VMExit triggered because of vmcs02

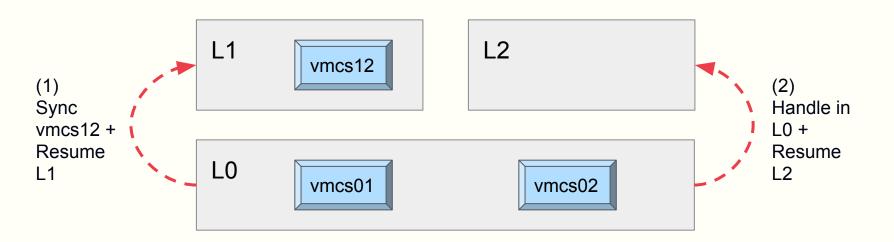

# L0 decides if to handle VMExit itself or reflect VMExit to L1

## nVMX event injection

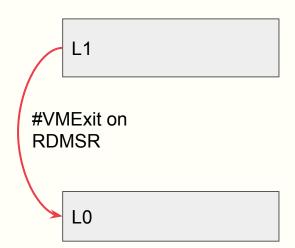

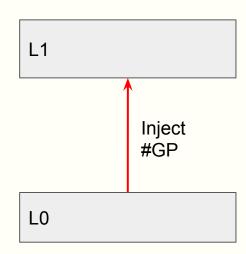

- 1. L1 RDMSR bad\_msr

- 2. RDMSR exits to L0

L1

- 1. L1 RDMSR bad\_msr

- RDMSR exits to L0

- 3. L0 emulates RDMSR and queues #GP:

- (a) Save pending exception in struct kvm\_vcpu\_arch

- (b) Set KVM\_REQ\_EVENT

L0 pending #GP

L1

- L1 RDMSR bad\_msr

- 2. RDMSR exits to L0

- 3. L0 emulates RDMSR and queues #GP:

- (a) Save pending exception in struct kvm\_vcpu\_arch

- (b) Set KVM REQ EVENT

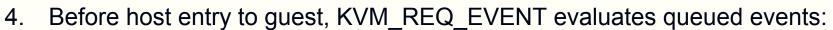

4. Before host entry to guest, KVM\_REQ\_EVENT evaluates queued events:

- L1 RDMSR bad\_msr

- 2. RDMSR exits to L0

- 3. L0 emulates RDMSR and queues #GP:

- (a) Save pending exception in struct kvm\_vcpu\_arch

- (b) Set KVM\_REQ\_EVENT

- Before host entry to guest, KVM\_REQ\_EVENT evaluates queued events:

Inject pending #GP to guest by VMCS

- L2 RDMSR bad\_msr

- RDMSR exits to L0

- 3. L0 emulates RDMSR and queues #GP:

- (a) Save pending exception in struct kvm\_vcpu\_arch

- (b) Set KVM\_REQ\_EVENT

- (a) If (vCPU in guest-mode && Has event which should L2→L1)

- ⇒ Emulate L2→L1

- (b) Otherwise ⇒ Inject pending #GP to guest by VMCS

- A VMExit can occur during event-delivery

- Example: Write of exception frame to stack triggers EPT\_VIOLATION

- A VMExit can occur during event-delivery

- Example: Write of exception frame to stack triggers EPT\_VIOLATION

- CPU saves the event which attempted to deliver in vmcs→idt\_vectoring\_info

- A VMExit can occur during event-delivery

- Example: Write of exception frame to stack triggers EPT\_VIOLATION

- CPU saves the event which attempted to deliver in vmcs→idt\_vectoring\_info

- On guest→host:

- 1. KVM checks if vmcs→idt\_vectoring\_info valid

- 2. If valid, queue injected event in struct kvm\_vcpu\_arch and set KVM\_REQ\_EVENT

- A VMExit can occur during event-delivery

- Example: Write of exception frame to stack triggers EPT\_VIOLATION

- CPU saves the event which attempted to deliver in vmcs→idt\_vectoring\_info

- On guest→host:

- 1. KVM checks if vmcs→idt\_vectoring\_info valid

- 2. If valid, queue injected event in struct kvm\_vcpu\_arch and set KVM\_REQ\_EVENT

- KVM\_REQ\_EVENT will evaluate injected event on next entry to guest

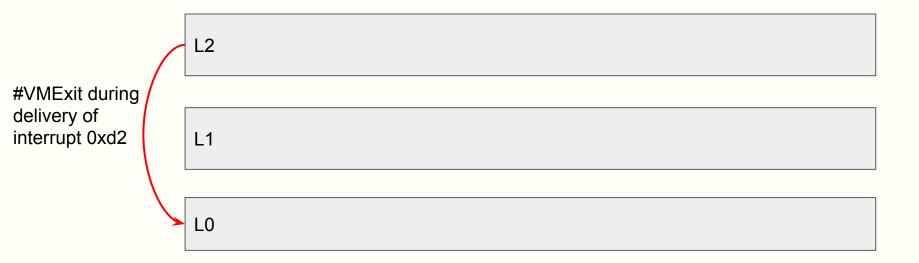

What if VMExit occurs during event-delivery to L2?

- What if VMExit occurs during event-delivery to L2?

- If exit reflected to L1 ⇒ Emulate exit during event-delivery to L1

- Emulate L2→L1 VMExit with injected event in vmcs12→idt\_vectoring\_info

- What if VMExit occurs during event-delivery to L2?

- If exit reflected to L1 ⇒ Emulate exit during event-delivery to L1

- Emulate L2→L1 VMExit with injected event in vmcs12→idt\_vectoring\_info

- Otherwise ⇒ Inject event directly to L2

- L1 should not intercept event!

- L1 should not be aware L0 had exit during attempt to deliver event

- What if VMExit occurs during event-delivery to L2?

- If exit reflected to L1 ⇒ Emulate exit during event-delivery to L1

- Emulate L2→L1 VMExit with injected event in vmcs12→idt\_vectoring\_info

- Otherwise ⇒ Inject event directly to L2

- L1 should not intercept event!

- L1 should not be aware L0 had exit during attempt to deliver event

- How does L0 know L1 can't intercept event on KVM\_REQ\_EVENT handler?

- What if VMExit occurs during event-delivery to L2?

- If exit reflected to L1 ⇒ Emulate exit during event-delivery to L1

- Emulate L2→L1 VMExit with injected event in vmcs12→idt\_vectoring\_info

- Otherwise ⇒ Inject event directly to L2

- L1 should not intercept event!

- L1 should not be aware L0 had exit during attempt to deliver event

- How does L0 know L1 can't intercept event on KVM\_REQ\_EVENT handler?

- nVMX requires clear separation between pending vs. injected!

- A pending event can be intercepted by L1

- An injected event cannot be intercepted by L1

## Example: nVMX event handling issue

Occasionally, L1 stuck after running L2 guests

#### Example: nVMX event handling issue

- Occasionally, L1 stuck after running L2 guests

- L1 dmesg reveals some hints on the issue

- All L1 CPUs but one waiting on KVM's mmu\_lock:

```

_raw_spin_lock+0x20/0x30

tdp_page_fault+0x1b1/0x260 [kvm]

? __remove_hrtimer+0x3c/0x90

kvm_mmu_page_fault+0x65/0x130 [kvm]

handle_ept_violation+0xaa/0x1a0 [kvm_intel]

```

#### Example: nVMX event handling issue

- Occasionally, L1 stuck after running L2 guests

- L1 dmesg reveals some hints on the issue

- All L1 CPUs but one waiting on KVM's mmu\_lock:

```

c _raw_spin_lock+0x20/0x30

tdp_page_fault+0x1b1/0x260 [kvm]

? __remove_hrtimer+0x3c/0x90

kvm_mmu_page_fault+0x65/0x130 [kvm]

handle_ept_violation+0xaa/0x1a0 [kvm_intel]

```

One L1 CPU is holding KVM's mmu lock while waiting for IPI ACK:

```

? smp_call_function_many+0x1c7/0x250

kvm_make_all_cpus_request+0xbb/0xd0 [kvm]

kvm_flush_remote_tlbs+0x1d/0x40 [kvm]

kvm_mmu_commit_zap_page+0x22/0xf0 [kvm]

mmu_free_roots+0x13c/0x150 [kvm]

```

```

qemu-system-x86-19066 [030] kvm_nested_vmexit: rip: Exit L2 to L0 0xfffff802c5dca82f reason: EPT_VIOLATION ext_inf1: 0x00000000000000182 ext_inf2: 0x00000000800000d2 ext_int: 0x00000000 ext_int_err: 0x000000000

```

⇒ L2→L0 exit during event-delivery of interrupt 0xd2

```

qemu-system-x86-19066 [030] kvm_nested_vmexit: rip: ← Exit L2 to L0

0xfffff802c5dca82f reason: EPT_VIOLATION ext_inf1: 0x00000000000000182

ext_inf2: 0x00000000800000d2 ext_int: 0x00000000 ext_int_err: 0x00000000

```

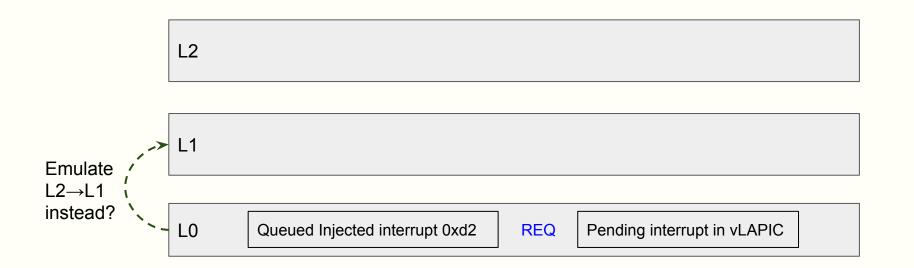

- ⇒ L2→L0 exit during event-delivery of interrupt 0xd2

- ⇒ L0 queues event for injection + Set KVM\_REQ\_EVENT

```

L1

L0 Queued Injected interrupt 0xd2 REQ

```

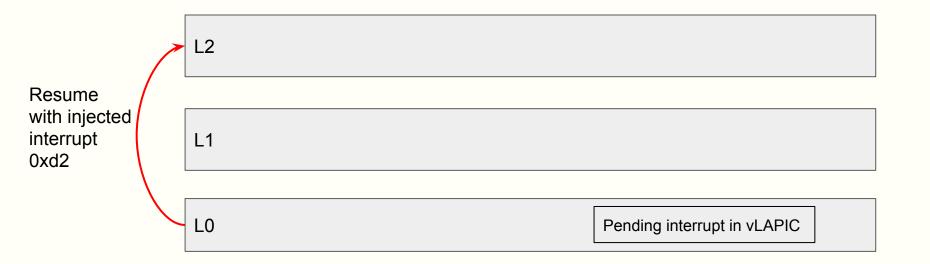

qemu-system-x86-19054 [028] kvm\_apic\_accept\_irq: apicid f vec 252 (Fixed|edge)

⇒ Received IPI queued pending interrupt 252 in L1 vLAPIC

L1

L0 Queued Injected interrupt 0xd2 REQ Pending interrupt in vLAPIC

```

qemu-system-x86-19066 [030] kvm_inj_virq: irq 210 \leftarrow re-inject interrupt to L2 qemu-system-x86-19066 [030] kvm_entry: vcpu 15 \leftarrow Resume L2

```

⇒ KVM\_REQ\_EVENT re-inject queued injected interrupt to L2

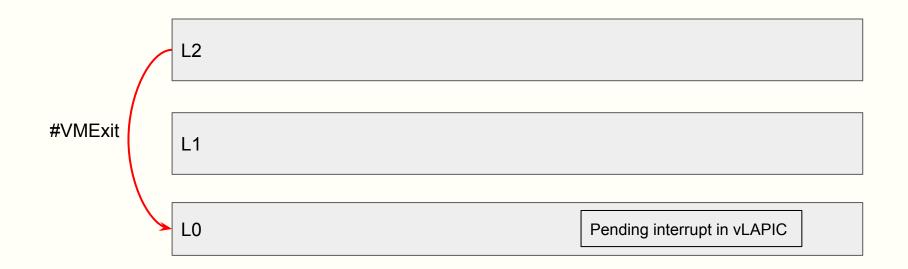

⇒ L2→L0 on EPT\_VIOLATION (not during event-delivery)

```

qemu-system-x86-19066 [030] kvm_nested_vmexit_inject: reason:

ext_int: 0x00000000 ext_int_err: 0x00000000

← Emulate exit from L2 to L1

gemu-system-x86-19066 [030] kvm_entry: vcpu 15 \epsilon Resume L1

```

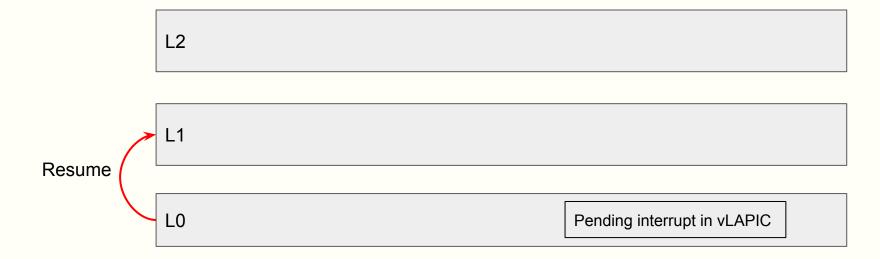

#### ⇒ L0 resumes L1

# ⇒ L0 resumes L1 pending L1 interrupt? Resume Pending interrupt in vLAPIC

- L0 didn't re-evaluate pending L1 event because KVM\_REQ\_EVENT not set

- IPI received when KVM\_REQ\_EVENT already set (Before re-injection to L2)

- L0 didn't re-evaluate pending L1 event because KVM\_REQ\_EVENT not set

- IPI received when KVM\_REQ\_EVENT already set (Before re-injection to L2)

- What if L0 will L2→L1 before resuming L2 with re-injection?

- L0 didn't re-evaluate pending L1 event because KVM\_REQ\_EVENT not set

- IPI received when KVM\_REQ\_EVENT already set (Before re-injection to L2)

- What if L0 will L2→L1 before resuming L2 with re-injection?

- ⇒ Queued injected event will be written to vmcs12->idt\_vectoring\_info

- L0 didn't re-evaluate pending L1 event because KVM\_REQ\_EVENT not set

- IPI received when KVM\_REQ\_EVENT already set (Before re-injection to L2)

- What if L0 will L2→L1 before resuming L2 with re-injection?

- ⇒ Queued injected event will be written to vmcs12->idt\_vectoring\_info

- ⇒ Bug: L1 will see exit on EXTERNAL\_INTERRUPT during event-delivery

- L0 didn't re-evaluate pending L1 event because KVM\_REQ\_EVENT not set

- IPI received when KVM\_REQ\_EVENT already set (Before re-injection to L2)

- What if L0 will L2→L1 before resuming L2 with re-injection?

- ⇒ Queued injected event will be written to vmcs12->idt\_vectoring\_info

- ⇒ Bug: L1 will see exit on EXTERNAL\_INTERRUPT during event-delivery

- We wish to inject to L2 and immediately after re-evaluate L1 pending event

- Sometimes KVM is blocked from exiting from L2 to L1:

- E.g. There is an injected event for L2

- Sometimes KVM is blocked from exiting from L2 to L1:

- E.g. There is an injected event for L2

- In these cases, we can request an "immediate-exit" from L2 to L0

- Sometimes KVM is blocked from exiting from L2 to L1:

- E.g. There is an injected event for L2

- In these cases, we can request an "immediate-exit" from L2 to L0

- "Immediate-exit" requests CPU to exit guest immediately after entering it

- Set KVM\_REQ\_EVENT

- Disable interrupts and sends Self-IPI, just before entering the guest

- Sometimes KVM is blocked from exiting from L2 to L1:

- E.g. There is an injected event for L2

- In these cases, we can request an "immediate-exit" from L2 to L0

- "Immediate-exit" requests CPU to exit guest immediately after entering it

- Set KVM\_REQ\_EVENT

- Disable interrupts and sends Self-IPI, just before entering the guest

- CPU will inject event and then immediately exit on EXTERNAL\_INTERRUPT

- When exit back to L0, re-evaluate L1 pending event

- Miss of L1 IPI when on L2→L0 exit during interrupt-delivery

- L1 stuck as a result of losing an IPI while holding KVM mmu\_lock

- Root-cause: Reinjection of L2 events blocked evaluation of L1 pending events

- 1a680e355c94 ("KVM: nVMX: Require immediate-exit when event reinjected to L2 and L1 event pending")

# Recent nVMX improvements

#### Mechanisms fixes

- nVMX event-injection fixes

- Missing L1 events, SMI while in guest-mode, handling L1 not intercepting interrupts

- <u>TODO:</u> Ability to get/set vCPU events considering pending/injected

- TODO: Keep CR2/DR6 unmodified if #PF/#DB intercepted by L1

- Jim Mattson series to handle all mentioned above: <a href="https://patchwork.kernel.org/project/kvm/list/?series=31593">https://patchwork.kernel.org/project/kvm/list/?series=31593</a>

- <u>TODO:</u> L2 pending trap exceptions can still be lost because of L2→L1 transition.

#### Nested APICv fixes

- Nested posted-interrupts race-condition and EOI-exitmap corruption

- Enabled running ESXi as L1 hypervisor with APICv enabled

- <u>TODO:</u> Use hardware for re-evaluation of missed nested posted-interrupts

- https://patchwork.kernel.org/patch/10132081/

- https://patchwork.kernel.org/patch/10132083/

#### Mechanisms fixes

- Nested VPID fixes & optimizations

- Invalidation of wrong TLB mappings and unnecessary TLB flushes

- Nested MMU optimizations

- L1<->L2 transitions avoid MMU unload, fast switch EPTP and L1/L2 separate MMU contextes

- L1→L2 VMEntry optimizations

- Dirty-track non-shadowed VMCS fields, faster build of vmcs02 MSR bitmap, optimize shadow VMCS copying

- Exposure of VMX features to guest fixes

- Affected by CPU features, KVM module parameters and guest CPUID!

- More L1→L2 VMEntry checks

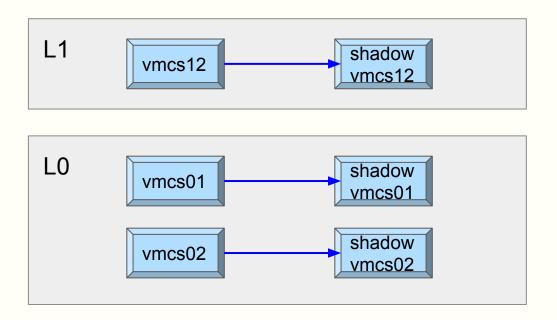

# New mechanism: nVMX Migration support

- KVM holds internal CPU state for running L2

- VMXON region address, active vmcs12 address

- Cached vmcs12 & cached shadow vmcs12

- Internal nested flags (E.g. nested\_run\_pending)

- Required IOCTLs to save/restore this state for migration

- KVM\_{GET,SET}\_NESTED\_STATE

- Required ability to set VMX MSRs from userspace

- <u>TODO</u>: QEMU patches for supporting this

- https://patchwork.kernel.org/patch/10601689/

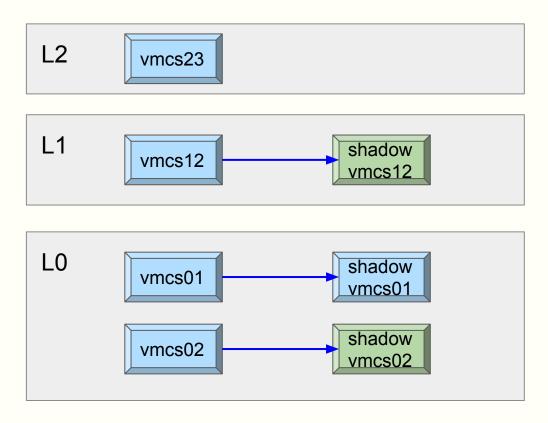

# New mechanism: VMCS Shadowing virtualization

- Use-case: Triple-Virtualization!

- Accelerate L2 VMREADs/VMWRITEs

# New mechanism: VMCS Shadowing virtualization

- Use-case: Triple-Virtualization!

- Accelerate L2 VMREADs/VMWRITEs

- However, L3 performance still insufficient for Oracle's production workloads

- See appendix slides for details

- <u>TODO</u>: Optimizations for VMCS Shadowing virtualization

- Avoid building vmcs02→{vmread,vmwrite}\_bitmap when vmcs12 bitmaps unchanged

- Cache CPU unsupported VMCS fields on KVM boot-time

- Get rid of cached shadow vmcs12

## Recent improvements have led to...

#### kvm-intel.nested=1 default on kernel 4.20!

https://patchwork.kernel.org/patch/10644311/

#### Future directions of nVMX

Microsoft Hyper-V improved nested perf by PV interface (eVMCS)

#### Future directions of nVMX

- Microsoft Hyper-V improved nested perf by PV interface (eVMCS)

- KVM should have it's own PV interface for nested

- eVMCS too coupled with Hyper-V PV interface

#### **Future directions of nVMX**

- Microsoft Hyper-V improved nested perf by PV interface (eVMCS)

- KVM should have it's own PV interface for nested

- eVMCS too coupled with Hyper-V PV interface

- Future of supporting all combinations of L0/L1 hypervisors PV interfaces?

- E.g. KVM was recently enhanced to be able to both use and expose Hyper-V eVMCS

- Should there be cross-hypervisor PV standard for nested-virtualization?

# Conclusion

#### Conclusion

- Many nVMX advancements over past year which we don't have time for...

- Appendix slides contain deep-dive to some of those mechanisms for reference!

- nVMX semantics stabilized very well over the past year

- Thanks to many contributors: Google, AWS, Intel, RedHat, Oracle and more

- Most semantic issues discovered by running various hypervisors as L1

- kvm-unit-tests VMX tests cover mainly edge cases and regression tests

- Challenges ahead: PV for nested & Triple-Virtualization

# Questions?

Thank you!

# Appendix

Things I wish I had time to present...:)

# **Appendix Outline**

- VMCS Shadowing

- Triple-Virtualization

- Nested APICv

- nVMX event injection

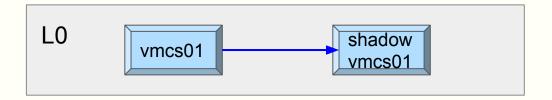

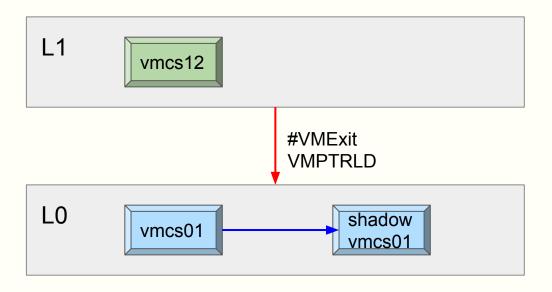

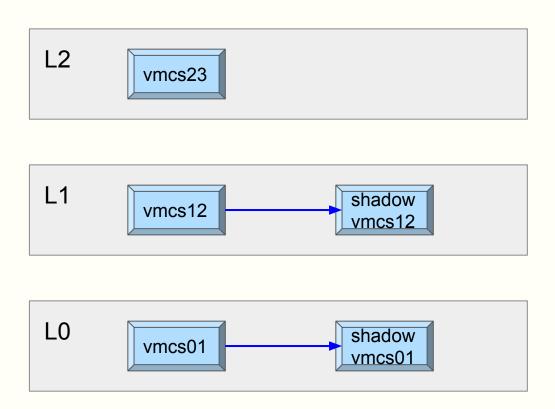

# VMCS Shadowing

#### VMCS cache

- On VMPTRLD, VMCS loaded to CPU is cached in per-CPU VMCS cache

- Access to VMCS done by dedicated instructions: VMREAD/VMWRITE

#### VMCS cache

- On VMPTRLD, VMCS loaded to CPU is cached in per-CPU VMCS cache

- Access to VMCS done by dedicated instructions: VMREAD/VMWRITE

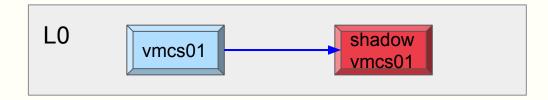

#### nVMX implementation:

- L0 VMPTRLD emulation copy in-memory vmcs12 into software cache

- L0 VMREAD/VMWRITE emulation read/write from/to cached vmcs12

- ⇒ Exits on L1's VMREAD/VMWRITE are significant performance hit

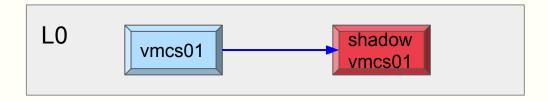

# **VMCS** Shadowing

- Hardware VMX feature to improve nVMX performance

- Reduce #VMExits on L1 VMREAD/VMWRITE

- VMCS->vmcs\_link\_ptr points to "shadow vmcs"

- L1 VMREAD/VMWRITE directed to "shadow vmcs"

- According to VMCS->{vmread,vmwrite}\_bitmap

# **VMCS** Shadowing usage

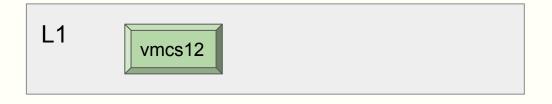

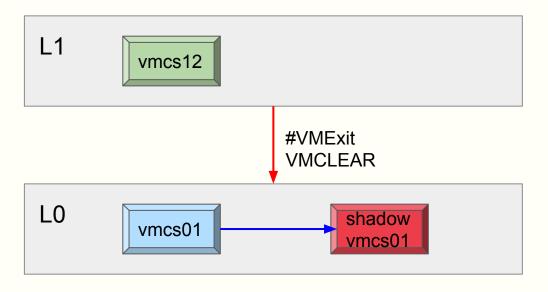

#### L1 VMPTRLD vmcs12

# L0 copies vmcs12 to shadow vmcs01

### L1 VMREAD/VMWRITE read/write shadow vmcs01

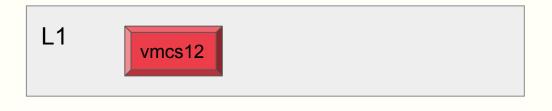

#### L0 VMCLEAR vmcs12

# L0 copies shadow vmcs01 to vmcs12

# VMCS Shadowing usage (Many copies...)

- On L1 VMPTRLD, L0 copies cached vmcs12 to shadow vmcs01

- L1 will read values using VMREAD from shadow vmcs01

- On L1 VMCLEAR, L0 copies shadow vmcs01 to cached vmcs12

- L1 may have modified shadow vmcs01 using VMWRITE

- On L1→L2 transition, L0 copies shadow vmcs01 to cached vmcs12

- L1 has written values using VMWRITE to shadow vmcs01

- On L2→L1 transition, L0 copies cached vmcs12 to shadow vmcs01

- L1 will read values using VMREAD from shadow vmcs01

# Triple-Virtualization!

### **Triple-Virtualization: Why?!**

- Some of Oracle Ravello guests are hypervisors themselves...

- ESXi, KVM, Xen, Hyper-V

- Therefore, setup is:

- L0 = Public cloud provider hypervisor

- L1 = Ravello's hypervisor (KVM based)

- L2 = Ravello guest which is a hypervisor (e.g. ESXi)

- L3 = L2 guests

- We are dealing with a Triple-Virtualization scenario!

### **Triple-Virtualization: VMCS Shadowing**

#### Virtualization

- Triple-Virtualization works but...

- L2 will execute VMREADs / VMWRITEs

- They will perform extremely poorly unless L1 is utilizing VMCS Shadowing

⇒ We need L0 to support VMCS Shadowing Virtualization!

- Lead us to contact Jim Mattson to implement this in GCE L0 KVM

- Jim developed the patches and I have further modified them for upstream

- https://www.spinics.net/lists/kvm/msg170724.html

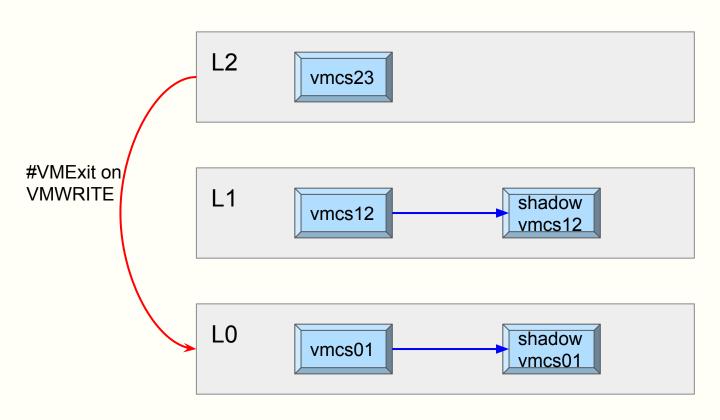

# **VMCS** Shadowing Emulation

#### L2 executes VMWRITE

### L0 examins vmcs12→vmwrite\_bitmap

# Option 1: VMWRITE intercepted by L1 by bitmap

# Option 2: L0 emulates VMWRITE on shadow vmcs12

### **VMCS Shadowing Emulation**

- All L2 VMREAD/VMWRITE still exit to L0

- Reflect exit on VMREAD/VMWRITE to L1 based on vmcs12→ {vmread,vmwrite}\_bitmap

- Modify L0 VMREAD/VMWRITE exit handlers to write to cached shadow vmcs12 instead of cached vmcs12 if vCPU in guest-mode

- Cache shadow vmcs12

- L1→L2: Copy from vmcs12→vmcs\_link\_ptr to shadow VMCS12 cache

- L2→L1: Flush shadow vmcs12 cache to guest vmcs12→vmcs\_link\_ptr

- 32c7acf04487 ("KVM: nVMX: Expose VMCS shadowing to L1 guest")

- ⇒ Saves exits to L1 on L2's VMREADs/VMWRITEs!

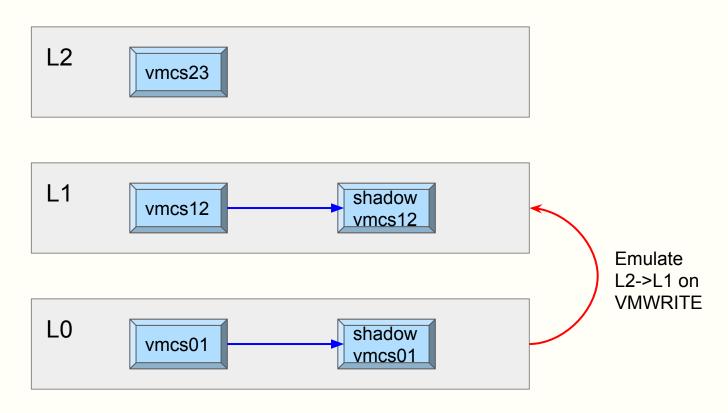

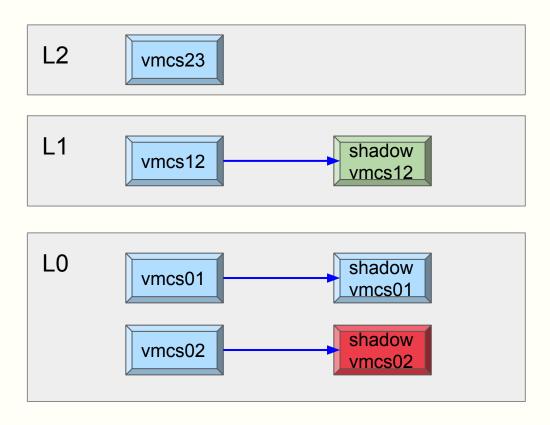

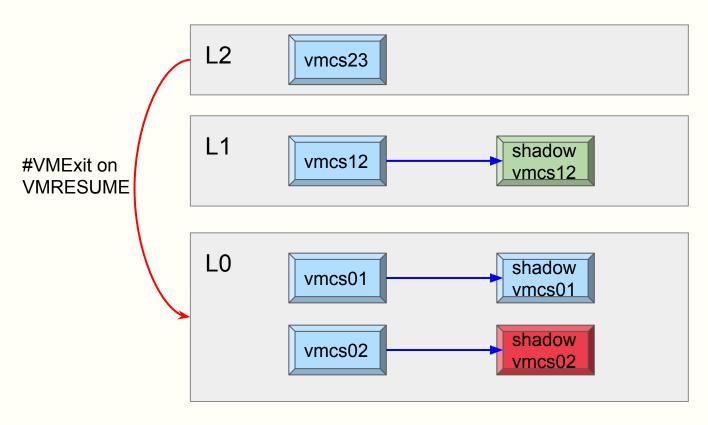

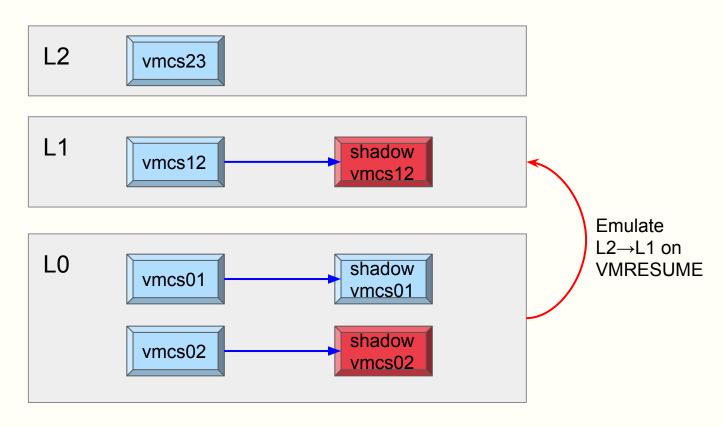

# **VMCS Shadowing Virtualization**

#### L1 executes VMRESUME

#### L0 creates vmcs02 with shadow vmcs

### L0 copies shadow vmcs12 to shadow vmcs02

#### L0 executes L2 with vmcs02

#### L2 executes VMWRITE writes to shadow vmcs02

#### L2 executes VMRESUME

# L0 copies shadow vmcs02 to shadow vmcs12

#### L0 forward exit on VMRESUME to L1

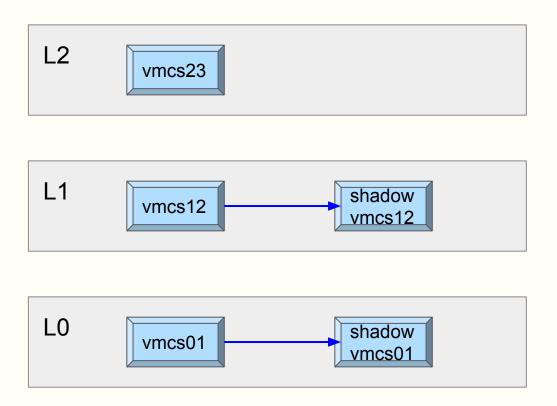

#### VMCS Shadowing Virtualization

- Allocate shadow VMCS and {vmread,vmwrite}\_bitmap for vmcs02

- vmcs02→{vmread,vmwrite}\_bitmap based on vmcs12 bitmaps

- Not identical as unsupported VMCS fields by L0 are still intercepted

- On L1→L2, copy cached shadow vmcs12 to shadow vmcs02

- On L2→L1, copy shadow vmcs02 to cached shadow vmcs12

- Not applied yet. v1 of patch series:

<a href="https://www.spinics.net/lists/kvm/msg170724.html">https://www.spinics.net/lists/kvm/msg170724.html</a>

- ⇒ Saves exits to both L0 & L1 on L2's VMREADs/VMWRITEs!

#### VMCS Shadowing usage: Many copies...

- On L1→L2 transition, L0 copies shadow vmcs01 to cached vmcs12

- On L2→L1 transition, L0 copies cached vmcs12 to shadow vmcs01

- On L1 VMPTRLD, L0 copies cached vmcs12 to shadow vmcs01

- On L1 VMCLEAR, L0 copies shadow vmcs01 to cached vmcs12

#### VMCS Shadowing Emulation: More copies...

- On L1→L2 transition, L0 copies shadow vmcs01 to cached vmcs12

And cache shadow vmcs12

- On L2→L1 transition, L0 copies cached vmcs12 to shadow vmcs01

And flush cached shadow vmcs12 to shadow vmcs12

- On L1 VMPTRLD, L0 copies cached vmcs12 to shadow vmcs01

- On L1 VMCLEAR, L0 copies shadow vmcs01 to cached vmcs12

#### VMCS Shadowing Virtualization: Even more copies!

- On L1→L2 transition, L0 copies shadow vmcs01 to cached vmcs12

And cache shadow vmcs12

And build vmcs02→{vmread,vmwrite}\_bitmap from vmcs12 bitmaps

And copy cached shadow vmcs12 to shadow vmcs02

- On L2→L1 transition, L0 copies cached vmcs12 to shadow vmcs01

And copy shadow vmcs02 to cached shadow vmcs12

And flush cached shadow vmcs12 to shadow vmcs12

- On L1 VMPTRLD, L0 copies cached vmcs12 to shadow vmcs01

- On L1 VMCLEAR, L0 copies shadow vmcs01 to cached vmcs12

### Triple-Virtualization insufficient performance

- L3→L2 results in a total of 15 copies!

- Of shadow vmcs to cached vmcs (/ cached shadow vmcs) and vice-versa

### Triple-Virtualization insufficient performance

- L3→L2 results in a total of 15 copies!

- Of shadow vmcs to cached vmcs (/ cached shadow vmcs) and vice-versa

#### Key Observations:

- 1. All transitions from/to Lx involves all underlying layers

- 2. Lx<->Ly involve copies of shadow vmcs to cached vmcs and vice-versa

- 3. Copies of shadow VMCS requires VMPTRLD which incur #VMExit

### Triple-Virtualization possible solutions

- Should create a KVM PV interface for nested? Similar to Hyper-V?

- Should there be cross-hypervisor PV standard for nested-virtualization?

- Supporting all combinations of L0/L1 hypervisors PV interfaces is complex...

- KVM was recently enhanced to be able to both use and expose Hyper-V eVMCS

- Can we suggest a new VMX feature for Intel to improve triple-virtualization?

- Ability to read/write from/to shadow VMCS without VMPTRLD to make it active?

\* Note: Deeper perf analysis wasn't performed yet

# Triple-Virtualization!

Technical details

#### VMCS Shadowing Virtualization: L3→L2

- L3 exits to L0 which decides to forward exit to L1

- L0 copy cached shadow vmcs12 to shadow vmcs12

- L0 copy cached vmcs12 to shadow vmcs01

- L0 resume into L1 which decides to forward exit to L2

- L1 copy cached shadow vmcs23 to shadow vmcs23

- L1 VMPTRLD vmcs12 which exit to L0

- L0 copy shadow vmcs01 to cached vmcs12

- L0 copy vmcs12 to cached vmcs12

- L0 copy vmcs12 to shadow vmcs02

- L1 copy cached vmcs23 to shadow vmcs12

- L1 VMPTRLD shadow vmcs12 which exit to L0

- L0 does 3 copies...

- L1 copies VMCS fields

- L1 VMCLEAR shadow vmcs12 which exit to L0

- L0 copies shadow vmcs01 to cached vmcs12

- L1 VMPTRLD vmcs12

- L0 does 3 copies...

## VMCS Shadowing Virtualization: L3→L2 (continue..)

- L1 resume into L2 exit to L0

- L0 copy shadow vmcs01 to cached vmcs12

- L0 copy shadow vmcs12 into cached shadow vmcs12

- And that's it! :)

#### Total of 15 copies!

(And we haven't counted L2→L3...)

## **Triple-Virtualization using Binary-Translation**

- HVX == Oracle Ravello binary-translation hypervisor

- L1 binary translation results in L3→L2 not involving L0

- Performance test setup:

- L0 = GCE\_KVM

- L1 = KVM / HVX (Haswell, 4 vCPUs, 26GB memory)

- L2 = KVM (8 vCPUs, 16GB memory)

- L2 is running 2 Ubuntu 16.04 guests as L3 (4 vCPUs, 8GB memory)

- netperf between L3 guests:

- HVX performs ~4x better than KVM both in throughput and latency

- Sysbench:

- HVX performs ~2x better then KVM

## Triple-Virtualization using eVMCS

- We can avoid shadow VMCS performance hit with PV interfaces

- Hyper-V eVMCS mechanism helps

- L0 emulate Hyper-V PV interface with eVMCS and L1 will consume it

- Probably was first one to run such a setup...

- Created patches for L0 QEMU to expose eVMCS

- Fixed bug: 2307af1c4b2e ("KVM: VMX: Mark VMXArea with revision\_id of physical CPU even when eVMCS enabled")

- Not a real solution for the general case

- Works only if L1 knows how to use eVMCS...

- We don't really want to expose Hyper-V PV interface for L1

- <u>TODO</u>: Collect concrete perf numbers

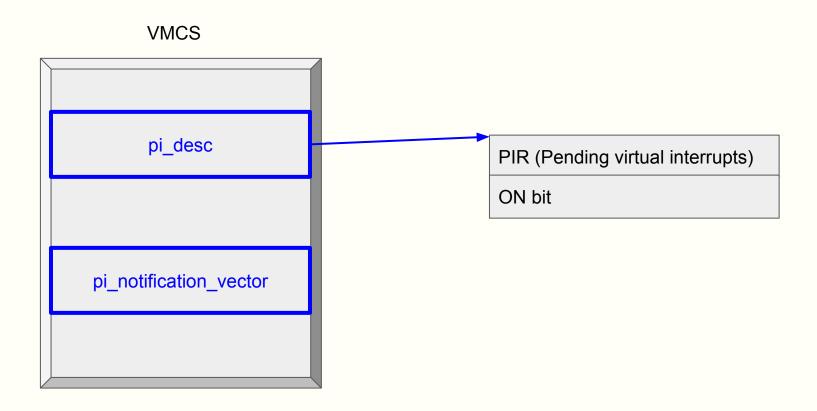

# Nested APICv

#### How APICv works?

- Generic name for combination of APIC related VMX features

- Aim to reduce #VMExits because of APIC and interrupts virtualization

#### **How APICv works?**

- APIC {access,register} Virtualization:

CPU emulates read/write from/to vLAPIC without #VMExit

- <u>Virtual interrupt delivery:</u>

CPU emulates LAPIC interrupt evaluation and delivery without #VMExit

- <u>Posted-Interrupts:</u>

Post interrupt to another CPU without #VMExit target CPU

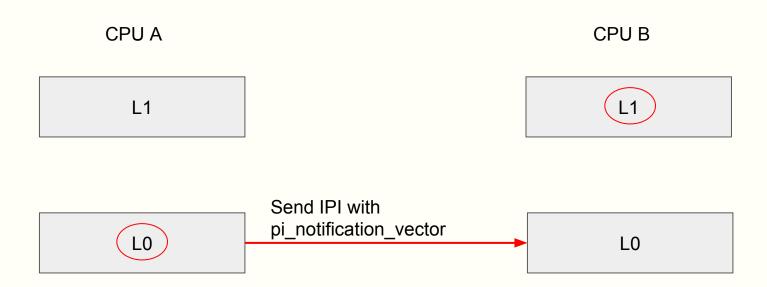

# How does posted-interrupts work?

# How does posted-interrupts work?

CPU A

CPU B

L1

L1

L0

L0

# How does posted-interrupts work?

1. Set bit in pi\_desc→PIR

2. Set pi\_desc→ON

CPU A

L1

L1

L0

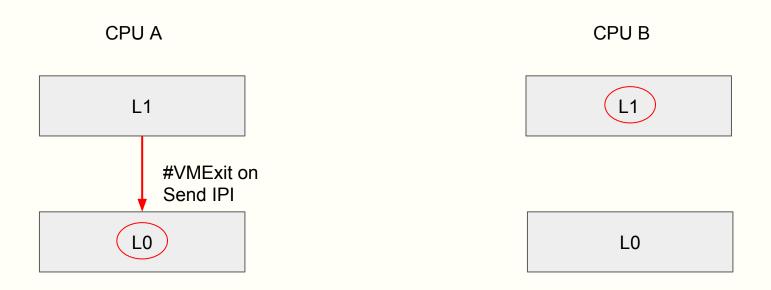

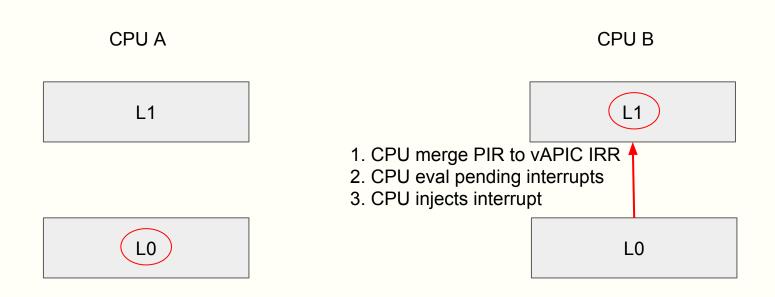

## How does posted-interrupts works?

- What if target CPU currently at L0?

- L0 needs to evaluate pending posted-interrupts in software

## How does posted-interrupts works?

- What if target CPU currently at L0?

- L0 needs to evaluate pending posted-interrupts in software

- ⇒ Before each entry to guest, sync PIR to LAPIC IRR

CPU A CPU B

L2

L1

L0

(L1)

L0

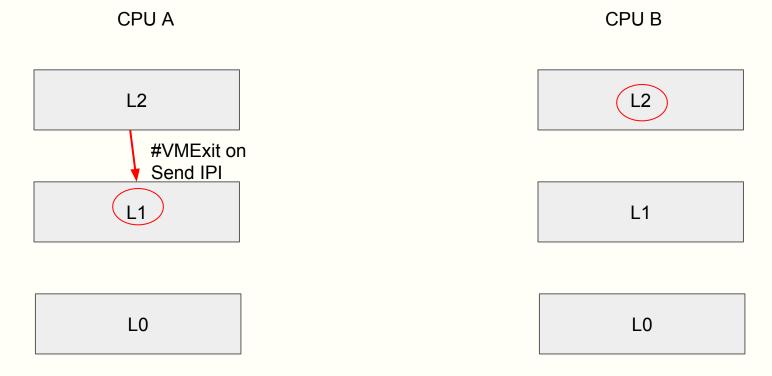

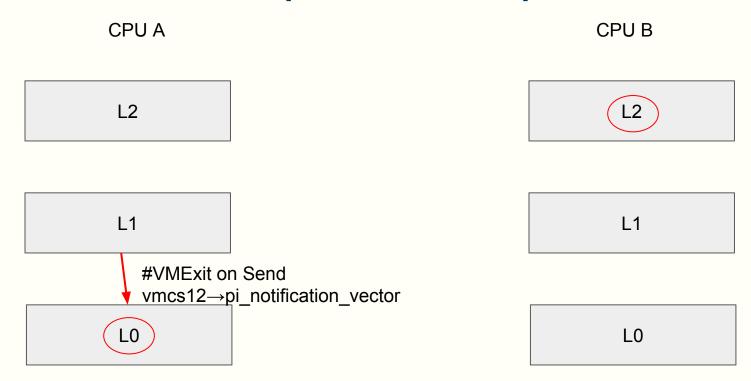

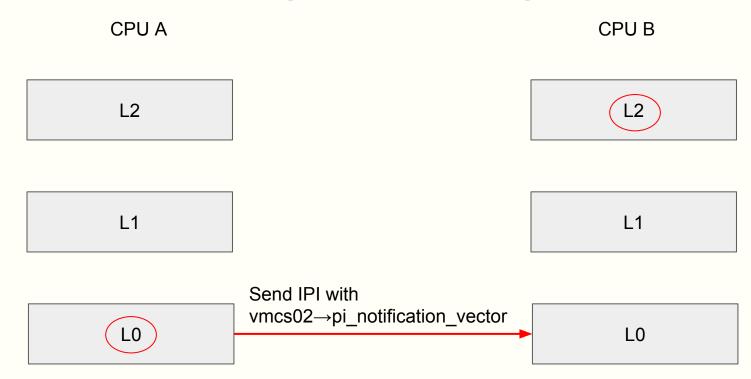

CPU A CPU B L2 **#VMExit** L1 L0

CPU A CPU B L2 L1 L1 **#VMExit on** Send IPI

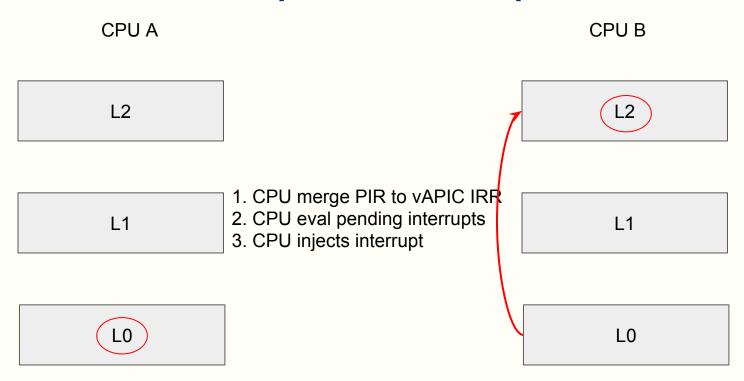

CPU A CPU B

L2

L1

L1

LO

L0

- 1. Set bit in pi\_desc→PIR

- 2. Set pi\_desc→ON

CPU A CPU B

L2

L1

L1

LO

LO

Sync PIR to LAPIC IRR

CPU A CPU B L2 **VMRESUME** L1 L1

CPU A CPU B

# What about the IPI

Sentto 17

LO

- L1 pending posted-interrupt needs to be evaluated before entry to L2!

- L1 intercepts external-interrupts ⇒ L0 should L2→L1

- Otherwise, inject interrupt directly to L2

- f27a85c4988d ("KVM: nVMX: Re-evaluate L1 pending events when running L2 and L1 got posted-interrupt")

```

diff --git a/arch/x86/kvm/vmx.c b/arch/x86/kvm/vmx.c

index 5ea482bb1b9c..5fe94e375d2d 100644

--- a/arch/x86/kvm/vmx.c

+++ b/arch/x86/kvm/vmx.c

@0 -8978,6 +8978,7 @0 static int vmx_sync_pir_to_irr(struct kvm_vcpu *vcpu)

struct vcpu vmx *vmx = to vmx(vcpu);

int max irr;

bool max irr updated:

WARN ON(!vcpu->arch.apicv active);

if (pi test on(&vmx->pi desc)) {

@@ -8987,7 +8988,16 @@ static int vmx sync pir to irr(struct kvm vcpu *vcpu)

* But on x86 this is just a compiler barrier anyway.

smp_mb_after_atomic();

max irr updated =

kvm apic update irr(vcpu, vmx->pi desc.pir, &max irr);

* If we are running L2 and L1 has a new pending interrupt

* which can be injected, we should re-evaluate

* what should be done with this new L1 interrupt.

if (is quest mode(vcpu) && max irr updated)

kvm vcpu exiting quest mode(vcpu):

} else {

max irr = kvm lapic find highest irr(vcpu);

```

CPU A CPU B L1 L1 L0 L0

CPU A CPU B L2 L1 1. Set bit in vmcs12→pi desc→PIR 2. Set vmcs12→pi\_desc→ON L0 L0

- What if target CPU currently at L0?

- Need to request L0 to evaluate pending nested posted-interrupts

- What if target CPU currently at L0?

- Need to request L0 to evaluate pending nested posted-interrupts

- ⇒ Signal pending nested-posted-interrupt and set KVM\_REQ\_EVENT

- What if target CPU currently at L0?

- Need to request L0 to evaluate pending nested posted-interrupts

- ⇒ Signal pending nested-posted-interrupt and set KVM\_REQ\_EVENT

- KVM\_REQ\_EVENT emulate nested-posted-interrupt delivery in software!

- Clear pi\_desc ON bit

- Sync pi\_desc→pir to L1 vLAPIC page

- Update vmcs02→guest intr status (RVI/SVI) accordingly

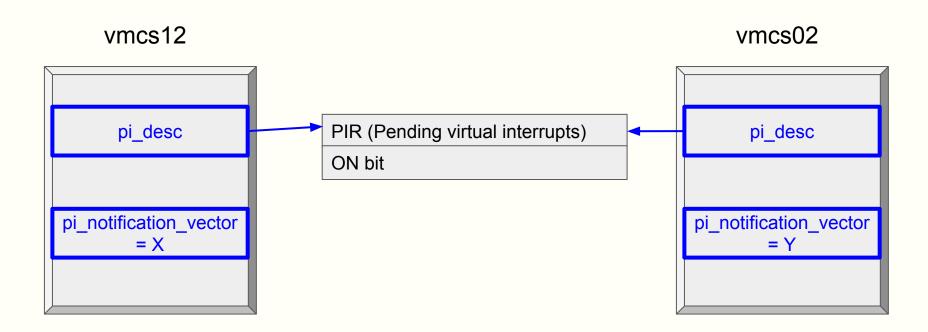

#### HW-assisted nested posted-interrupt

- Software emulation error prone and less efficient

- Could mistakenly diverge from hardware implementation

- <u>TODO:</u> Bug: If target vCPU exits to L1 after sender sets pi\_pending, than notification-vector interrupt is not raised to L1!

- <u>TODO</u>: Get rid of pi\_pending and instead use L1 LAPIC IRR as CPU does

- <u>TODO</u>: Install host handler for vmcs02→pi\_notification\_vector to avoid missing pending interrupt

- <u>TODO</u>: Trigger CPU posted-interrupt logic by self-IPI in case of pending nested posted interrupt

#### HW-assisted nested posted-interrupt

- https://patchwork.kernel.org/patch/10132081/

- https://patchwork.kernel.org/patch/10132083/

## Example 2: Nested posted-interrupt issue

- Race-Condition in delivering nested Posted-Interrupts

- Root-cause: Delivering event in non-standard way

- Should use kvm\_make\_request() + kvm\_vcpu\_kick()

- 6b6977117f50 ("KVM: nVMX: Fix races when sending nested PI while dest enters/leaves L2")

## How does virtual interrupt delivery works?

- VMCS—guest\_intr\_status specifies:

- 1. RVI: Holds pending virtual interrupt vector

- 2. <u>SVI:</u> Holds in-service virtual interrupt vector

- Certain actions cause evaluation of pending virtual interrupts

- VMEntry, Write to TPR, Write to EOI, Self-IPI and posted-interrupts processing

## How does virtual interrupt delivery works?

- VMCS—guest\_intr\_status specifies:

- 1. RVI: Holds pending virtual interrupt vector

- 2. SVI: Holds in-service virtual interrupt vector

- Certain actions cause evaluation of pending virtual interrupts

- VMEntry, Write to TPR, Write to EOI, Self-IPI and posted-interrupts processing

- VMCS—eoi\_exitmap defines vectors on which EOI will cause VMExit in addition to EOI virtualization

- o In order to emulate LAPIC EOI broadcast to IOAPIC EOI

# How does KVM use virtual interrupt delivery?

On entry to guest, set RVI to highest vector set in vLAPIC IRR

## How does KVM use virtual interrupt delivery?

- On entry to guest, set RVI to highest vector set in vLAPIC IRR

- Write to IOAPIC redir-table request KVM\_REQ\_SCAN\_IOAPIC on all vCPUs

- Configure VMCS->eoi\_exitmap according to vectors IOAPIC require EOI broadcast on

## How does KVM use virtual interrupt delivery?

- On entry to guest, set RVI to highest vector set in vLAPIC IRR

- Write to IOAPIC redir-table request KVM\_REQ\_SCAN\_IOAPIC on all vCPUs

- Configure VMCS->eoi\_exitmap according to vectors IOAPIC require EOI broadcast on

- Nested virtual interrupt delivery is "trivial"

- o vmcs02→guest\_intr\_status = vmcs12→guest\_intr\_status

- o vmcs02→eoi\_exitmap = vmcs12→eoi\_exitmap

- Disable WRMSR intercept on LAPIC EOI and SELF\_IPI

ESXi running as L1 which runs L2 guests loses network connectivity

- ESXi running as L1 which runs L2 guests loses network connectivity

- Setting enable\_apicv=0 seems to make problem disappear

- ESXi running as L1 which runs L2 guests loses network connectivity

- Setting enable\_apicv=0 seems to make problem disappear

- Analysis shows IOAPIC never got EOI for previous NIC IRQ

- ESXi running as L1 which runs L2 guests loses network connectivity

- Setting enable\_apicv=0 seems to make problem disappear

- Analysis shows IOAPIC never got EOI for previous NIC IRQ

- L0 KVM event trace shows:

- ESXi running as L1 which runs L2 guests loses network connectivity

- Setting enable\_apicv=0 seems to make problem disappear

- Analysis shows IOAPIC never got EOI for previous NIC IRQ

- L0 KVM event trace shows:

- 1. ESXi kernel modifies IOAPIC redir-table (IOAPIC Steering)

- ESXi running as L1 which runs L2 guests loses network connectivity

- Setting enable\_apicv=0 seems to make problem disappear

- Analysis shows IOAPIC never got EOI for previous NIC IRQ

- L0 KVM event trace shows:

- 1. ESXi kernel modifies IOAPIC redir-table (IOAPIC Steering)

- 2. Write to IOAPIC requests KVM\_REQ\_SCAN\_IOAPIC on all L1 vCPUs

- ESXi running as L1 which runs L2 guests loses network connectivity

- Setting enable\_apicv=0 seems to make problem disappear

- Analysis shows IOAPIC never got EOI for previous NIC IRQ

- L0 KVM event trace shows:

- 1. ESXi kernel modifies IOAPIC redir-table (IOAPIC Steering)

- 2. Write to IOAPIC requests KVM\_REQ\_SCAN\_IOAPIC on all L1 vCPUs

- 3. One CPU runs SCAN\_IOAPIC handler while vCPU in guest-mode!

- ESXi running as L1 which runs L2 guests loses network connectivity

- Setting enable\_apicv=0 seems to make problem disappear

- Analysis shows IOAPIC never got EOI for previous NIC IRQ

- L0 KVM event trace shows:

- 1. ESXi kernel modifies IOAPIC redir-table (IOAPIC Steering)

- 2. Write to IOAPIC requests KVM\_REQ\_SCAN\_IOAPIC on all L1 vCPUs

- 3. One CPU runs SCAN\_IOAPIC handler while vCPU in guest-mode!

- ⇒ Will update eoi\_exitmap of vmcs02 instead of vmcs01!

- 4. L1 NIC IRQ EOI will not exit to L0 and thus won't propagate to IOAPIC

- IOAPIC never got EOI for previous NIC IRQ

- Issue found only when running ESXi as L1

- Many issues caused by ESXi IOAPIC steering mechanism...

- Root-cause: IOAPIC EOI-exitmap code not adjusted to nested case

- Update of EOI-exitmap should be delayed to when vCPU is running L1

- Handle case LAPIC & IOAPIC are pass-through by updating

vcpu->arch.ioapic\_handled\_vectors and only delay update of EOI-exitmap

- e40ff1d6608d ("KVM: nVMX: Do not load EOI-exitmap while running L2")

```

@@ -7124,6 +7122,20 @@ static void vcpu scan ioapic(struct kvm vcpu *vcpu)

kvm x86 ops->svnc pir to irr(vcpu):

kvm ioapic scan entry(vcpu, vcpu->arch.ioapic handled vectors);

if (is guest mode(vcpu))

vcpu->arch.load eoi exitmap pending = true;

else

kvm make request(KVM_REQ_LOAD_EOI_EXITMAP, vcpu);

+static void vcpu load eoi exitmap(struct kvm vcpu *vcpu)

u64 eoi exit bitmap[4]:

if (!kvm apic hw enabled(vcpu->arch.apic))

return;

bitmap_or((ulong *)eoi_exit_bitmap, vcpu->arch.ioapic_handled_vectors,

vcpu to synic(vcpu)->vec bitmap, 256);

kvm x86 ops->load eoi exitmap(vcpu, eoi exit bitmap);

00 - 7238, 6 + 7250, 8 00 static int vcpu enter quest(struct kvm vcpu *vcpu)

if (kvm check request(KVM REQ SCAN IOAPIC, vcpu))

vcpu scan ioapic(vcpu);

if (kvm check request(KVM REQ LOAD EOI EXITMAP, vcpu))

vcpu load eoi exitmap(vcpu);

```

- vCPU should not halt when L1 is injecting events to L2

- Root-Cause: Not checking if VMEntry is vectoring when guest activity state is set to HLT

- 135a06c3a515 ("KVM: nVMX: Don't halt vcpu when L1 is injecting events to L2")

- Should also wake blocked vCPU while in guest-mode if pending RVI

- Evaluating pending vCPU events should include check if RVI[7:4] > vPPR[7:4]

- e6c67d8cf117 ("KVM: nVMX: Wake blocked vCPU in guest-mode if pending interrupt in virtual APICv")

- Direct interrupt injection to L2 doesn't update L1 LAPIC IRR and ISR and doesn't consider PPR

- Root-cause: Not using standard inject\_pending\_event() event injection framework for injecting interrupt directly to L2

- 851c1a18c541 ("KVM: nVMX: Fix injection to L2 when L1 don't intercept external-interrupts")

# nVMX event injection

More issues...

1. L2 RDMSR bad\_msr which exits to L0

- 1. L2 RDMSR bad\_msr which exits to L0

- 2. L1 doesn't intercept MSR and thus RDMSR emulated by L0

- 1. L2 RDMSR bad\_msr which exits to L0

- 2. L1 doesn't intercept MSR and thus RDMSR emulated by L0

- 3. L0 queues a pending #GP exception

- L2 RDMSR bad\_msr which exits to L0

- 2. L1 doesn't intercept MSR and thus RDMSR emulated by L0

- 3. L0 queues a pending #GP exception

- 4. L0 KVM\_REQ\_EVENT evaluates what should be done with queued events:

- a. L1 doesn't intercept #GP

- b. L1 has pending interrupt in LAPIC (Other L1 CPU sent IPI)

- L2 RDMSR bad\_msr which exits to L0

- L1 doesn't intercept MSR and thus RDMSR emulated by L0

- 3. L0 queues a pending #GP exception

- 4. L0 KVM\_REQ\_EVENT evaluates what should be done with queued events:

- a. L1 doesn't intercept #GP

- b. L1 has pending interrupt in LAPIC (Other L1 CPU sent IPI)

- 5. L0 emulates L2→L1 on EXTERNAL\_INTERRUPT

- L2 RDMSR bad\_msr which exits to L0

- 2. L1 doesn't intercept MSR and thus RDMSR emulated by L0

- 3. L0 queues a pending #GP exception

- 4. L0 KVM\_REQ\_EVENT evaluates what should be done with queued events:

- a. L1 doesn't intercept #GP

- b. L1 has pending interrupt in LAPIC (Other L1 CPU sent IPI)

- 5. L0 emulates L2→L1 on EXTERNAL\_INTERRUPT

- 6. Exception still pending in struct kvm\_vcpu\_arch

- ⇒ Will be injected to L1 on next KVM\_REQ\_EVENT!

- L2 exception injected into L1!

- Root-cause: Not clearing exception.pending on L2→L1 transition

- Bug mistakenly introduced when exception.injected was added

- Fix: Clear pending exception on L2→L1

- 5c7d4f9ad39d ("KVM: nVMX: Fix bug of injecting L2 exception into L1")

- L2 exception injected into L1!

- Root-cause: Not clearing exception.pending on L2→L1 transition

- Bug mistakenly introduced when exception.injected was added

- Fix: Clear pending exception on L2→L1

- 5c7d4f9ad39d ("KVM: nVMX: Fix bug of injecting L2 exception into L1")

- OK to clear exception.pending?

- A pending exception will be re-triggered\* on next resume of L2

- \* TODO: L2 pending trap exceptions can still be lost...